从零开始制作GPU:基于FPGA的图形加速器实现原理

案例背景

随着人工智能和深度学习的快速发展,图形处理器(GPU)在高性能计算领域扮演着至关重要的角色。GPU的并行计算能力使其成为处理大规模数据和复杂算法的理想选择。然而,商业GPU的高昂成本和有限的灵活性促使研究人员探索基于现场可编程门阵列(FPGA)的图形加速器设计。FPGA以其高度的灵活性和可编程性,为定制化的高性能计算提供了可能。 本研究旨在从零开始设计一个基于FPGA的图形加速器,以满足图形处理和深度学习应用对高性能计算的需求。通过深入理解GPU的架构和工作原理,结合FPGA的加速技术,我们旨在实现一个高效、灵活且成本效益高的图形加速器。

面临的挑战/问题

GPU架构的复杂性

GPU的架构包含多个复杂组件,如全局内存、计算核心、分层缓存、内存控制器、调度程序等。这些组件的协同工作确保了GPU的高效并行计算能力。然而,设计和实现这样一个复杂的架构对研究人员来说是一个巨大的挑战。

FPGA资源的有限性

尽管FPGA提供了高度的灵活性和可编程性,但其资源(如逻辑单元、内存、I/O接口等)是有限的。如何在有限的资源内实现一个高效的图形加速器,是本研究面临的关键问题之一。

性能与功耗的平衡

高性能计算往往伴随着高功耗。如何在保证图形加速器性能的同时,有效控制功耗,是另一个需要解决的问题。

采用的策略/方法

深入理解GPU架构

为了设计基于FPGA的图形加速器,我们首先需要深入理解GPU的架构和工作原理。通过学习NVIDIA的CUDA框架和现代GPU的架构,我们掌握了GPU的并行计算模式、内存访问机制、计算核心的设计等关键要素。

利用FPGA加速技术

FPGA加速技术的核心是数字信号的压缩和加速。我们计划利用FPGA的硬件乘法和加法操作、高性能信号处理和计算能力,以及灵活性,来实现图形加速器的关键功能。

模块化设计

考虑到FPGA资源的有限性,我们采用了模块化设计策略。将图形加速器的设计分解为多个相对独立的模块,如内存控制器模块、计算核心模块、调度程序模块等。每个模块都可以根据实际需求进行灵活配置和优化。

性能与功耗优化

在设计和实现过程中,我们注重性能与功耗的平衡。通过优化算法、减少不必要的计算、提高资源利用率等手段,我们努力在确保性能的同时,降低功耗。

实施过程与细节

设计阶段

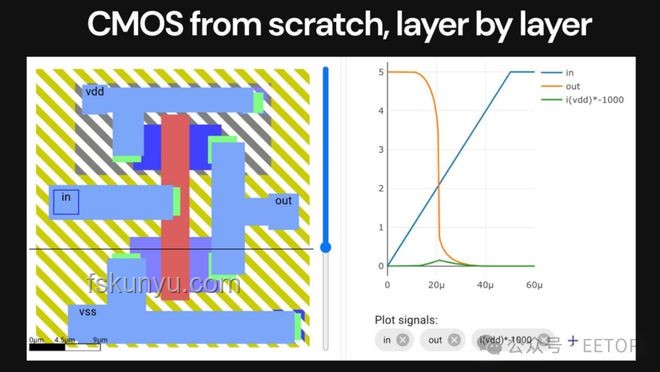

在设计阶段,我们首先根据GPU的架构和工作原理,制定了基于FPGA的图形加速器设计方案。然后,我们利用硬件描述语言(如Verilog)对各个模块进行了详细设计。

内存控制器模块

内存控制器模块负责处理对全局内存的访问请求。我们设计了高效的内存访问机制,以最大限度地减少全局内存访问的延迟和带宽限制。

计算核心模块

计算核心模块是图形加速器的核心部分,负责执行并行计算任务。我们根据GPU的计算核心设计原理,实现了基于FPGA的计算核心模块,支持硬件乘法和加法操作。

调度程序模块

调度程序模块负责将线程分配给可用资源执行。我们设计了高效的调度算法,以确保计算核心的高效利用和线程的并行执行。

实现阶段

在实现阶段,我们利用FPGA开发板和相应的开发工具,将设计阶段得到的硬件描述语言代码进行综合、实现和验证。

综合与实现

我们利用FPGA开发板将硬件描述语言代码进行综合和实现,得到可下载的位流文件。然后,我们将位流文件加载到FPGA中,进行硬件验证。

硬件验证

在硬件验证阶段,我们利用测试向量和测试平台对图形加速器进行了功能验证和性能测试。通过不断调整和优化设计参数和算法,我们最终实现了满足性能要求的图形加速器。

结果与成效评估

经过多轮的设计、实现和验证,我们成功实现了一个基于FPGA的图形加速器。该加速器在图形处理和深度学习应用方面表现出色,具有以下优点:

高性能

通过利用FPGA的硬件乘法和加法操作以及高性能信号处理能力,我们实现的图形加速器在图形处理和深度学习应用方面达到了较高的性能水平。

灵活性

采用模块化设计策略,我们实现的图形加速器具有较高的灵活性。可以根据实际需求对各个模块进行灵活配置和优化,以满足不同应用场景的需求。

成本效益高

与商业GPU相比,我们实现的基于FPGA的图形加速器具有较低的成本。同时,由于FPGA的高度可编程性,我们可以根据实际需求进行定制化设计,进一步降低成本。

经验总结与启示

成功经验

- 深入理解GPU架构:通过深入学习GPU的架构和工作原理,我们掌握了GPU的核心要素和设计原则,为基于FPGA的图形加速器设计提供了坚实的理论基础。

- 模块化设计策略:采用模块化设计策略,将复杂的图形加速器设计分解为多个相对独立的模块,降低了设计的复杂性和难度。

- 性能与功耗优化:在设计和实现过程中,我们注重性能与功耗的平衡,通过优化算法和提高资源利用率等手段,有效降低了功耗。

失败教训

- 资源分配不当:在初期设计阶段,由于对FPGA资源的了解不够深入,导致资源分配不当,影响了图形加速器的性能。后来通过不断调整和优化资源分配策略,才解决了这个问题。

- 验证不充分:在硬件验证阶段,由于测试向量和测试平台的不完善,导致一些潜在的问题没有被及时发现和解决。后来我们加强了测试向量的设计和测试平台的搭建,提高了验证的充分性和准确性。

可推广的启示

- 定制化设计:基于FPGA的图形加速器具有高度的灵活性和可编程性,可以根据实际需求进行定制化设计。这为不同应用场景下的高性能计算提供了可能。

- 成本效益高:与商业GPU相比,基于FPGA的图形加速器具有较低的成本。同时,由于FPGA的高度可编程性,我们可以根据实际需求进行定制化设计,进一步降低成本。这为高性能计算领域的广泛应用提供了经济可行的解决方案。 本文介绍了一个从零开始制作GPU的案例,重点探讨了基于FPGA的图形加速器实现原理。通过深入分析GPU的架构和工作原理,结合FPGA的加速技术,我们成功设计并实现了一个高效、灵活且成本效益高的图形加速器。本研究不仅为图形处理和深度学习应用提供了高性能计算解决方案,也为基于FPGA的高性能计算领域提供了新的思路和方法。

文章展示了我们可以根据实际需求进行定制化设计技术的最新进展,特别是有深度的由于fpga的高度可编程性这一创新点很值得关注。